在当今高度集成的电子系统中,单电源供电已成为主流趋势,因其能够简化电源管理、降低成本并减少系统体积。CMOS(互补金属氧化物半导体)集成电路以其低功耗、高噪声容限和易于集成的优势,成为实现单电源接口电路设计的理想选择。本文将探讨基于CMOS技术的单电源接口电路设计原理、关键模块及设计考量。

一、 单电源接口电路设计基础

单电源接口电路的核心挑战在于处理信号摆幅和共模电平的兼容性。在单电源供电(例如+5V或+3.3V)下,信号的动态范围被限制在0V至VDD之间。而许多传感器、外部器件或通信标准(如RS-232传统电平)产生的信号可能包含负电压或超出此范围的电压。因此,接口电路必须完成电平转换、信号调理和阻抗匹配等功能,同时确保自身在单电源下稳定工作。

CMOS技术在此类设计中展现出独特优势:

- 宽电源电压范围:许多CMOS工艺支持较宽的VDD范围,便于适应不同的单电源标准。

- 轨到轨(Rail-to-Rail)输入/输出能力:通过特殊设计的输入级和输出级,CMOS运放和逻辑电路可以实现输入和输出电压非常接近电源轨(0V和VDD),最大化信号动态范围。

- 高输入阻抗:CMOS器件的栅极输入阻抗极高,对前级电路的负载效应极小,有利于信号采集。

二、 关键电路模块设计

一个典型的单电源接口电路通常包含以下几个关键模块:

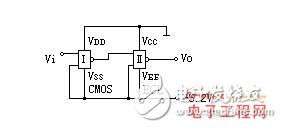

1. 电平移位器(Level Shifter):

这是处理不同逻辑电平(如1.8V CMOS与3.3V TTL)之间接口的核心。设计时需考虑电压转换方向、速度及功耗。常用结构包括使用串联NMOS/PMOS对、交叉耦合锁存器或基于运放的加法器电路,确保信号在0-VDD范围内被准确平移和整形。

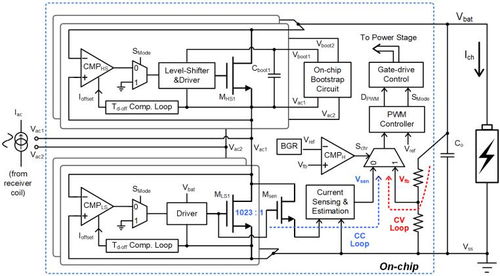

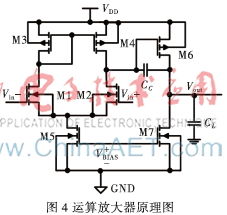

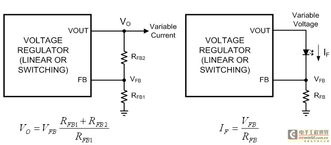

2. 单电源运算放大器接口:

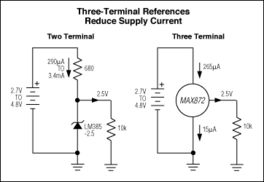

用于模拟信号调理(如放大、滤波)。设计重点在于设置合适的直流偏置点(通常为VDD/2),以确保交流信号在单电源下能以该点为参考进行双向摆动。这通常通过电阻分压网络或专用基准电压源(如带隙基准)实现。输入级需采用轨到轨或伪轨到轨结构以接收地电位附近的信号。

3. 模拟开关与多路复用器:

在CMOS工艺中,模拟开关由MOSFET构成,其导通电阻(RON)和开关速度是关键参数。单电源设计需确保开关在全部输入信号范围内(0-VDD)都能保持低且平坦的RON,并注意电荷注入和时钟馈通效应的影响。

4. 输入/输出(I/O)缓冲器:

用于驱动外部负载(如LED、继电器或传输线)。设计需提供足够的驱动电流,同时具备过压保护、静电放电(ESD)防护和缓变边沿控制(以减少EMI)。在单电源下,输出级常采用推挽(Push-Pull)CMOS结构以实现接近电源轨的输出摆幅。

三、 设计考量与挑战

- 电源噪声与去耦:单电源系统对电源噪声更敏感,尤其是在模拟电路部分。必须在VDD和地之间靠近芯片电源引脚处放置适当容值的去耦电容,以滤除高频噪声并提供局部电荷储备。

- 信号完整性:单电源下,信号的地电位参考至关重要。需要精心设计接地策略(如模拟地、数字地分离并通过单点连接),避免地弹噪声影响敏感模拟接口。对于高速接口,还需考虑阻抗匹配和传输线效应。

- 功耗与性能权衡:虽然CMOS静态功耗低,但在接口电路频繁切换时,动态功耗不可忽视。设计时需根据应用需求优化电路结构(如选择适当的驱动强度、采用时钟门控)以平衡速度与功耗。

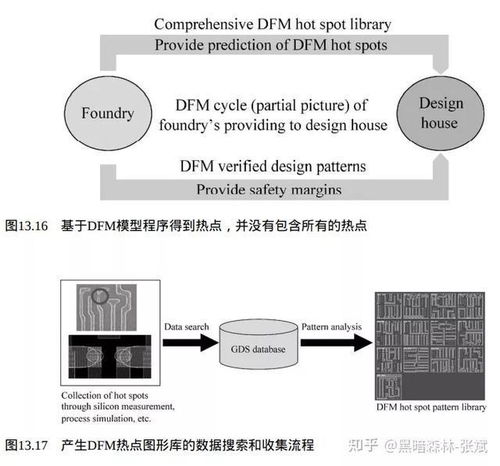

- 工艺角与可靠性:设计必须考虑工艺偏差、温度变化和电源电压波动对电路性能(如偏置点、增益、延迟)的影响,通过仿真覆盖各种极端条件(Corner Case),并留出足够的设计余量。

四、

基于CMOS集成电路的单电源接口电路设计是现代电子系统实现高效、紧凑互联的关键。通过充分利用CMOS技术的优势,并精心设计电平移位、信号调理、驱动保护等模块,可以有效解决单电源环境下的信号兼容性问题。成功的接口设计不仅需要深入理解电路原理,还需综合考虑噪声、功耗、工艺和可靠性等系统级因素,从而在芯片层面实现稳定、鲁棒且成本优化的接口解决方案。随着CMOS工艺的不断进步,未来单电源接口电路将向着更低电压、更高速度和更智能集成的方向持续发展。