在当今高速发展的数字集成电路(IC)设计领域,硬件描述语言(HDL)已成为连接抽象概念与物理实现的桥梁。由蔡觉平教授编著、西安电子科技大学出版社出版的《Verilog HDL数字集成电路高级程序设计》(ISBN:9787560638584)正是这样一部旨在引导读者从掌握基础语法跨越至高级设计实践的权威著作。

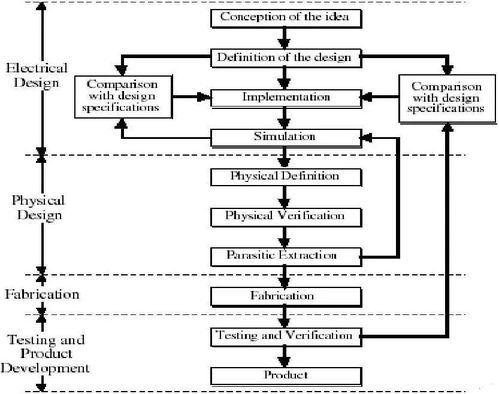

本书并非简单的语法手册,其核心价值在于“高级程序设计”的定位。作者蔡觉平教授凭借在微电子领域的深厚学术积淀与工程经验,系统性地构建了从Verilog HDL核心语法、可综合编码风格、到复杂数字系统建模与验证的知识体系。书中不仅详细讲解了组合逻辑、时序逻辑、有限状态机(FSM)等基础模块的描述方法,更深入探讨了如何用Verilog进行算法级建模、流水线设计、低功耗设计以及可测试性设计等高级主题。这些内容紧密贴合工业界对高性能、高可靠性数字芯片的设计需求。

一个显著的特色是理论与实践的结合。书中包含了大量经过精心设计的示例代码和综合实例,如FIR滤波器、微处理器核心部件等,这些案例能有效帮助读者理解如何将抽象的硬件功能转化为高效、可综合的RTL(寄存器传输级)代码。本书对仿真、调试技巧以及常见的设计陷阱也有专门论述,这对于培养工程师严谨的设计思维和调试能力至关重要。

对于读者而言,无论是高等院校电子工程、微电子专业的研究生和高年级本科生,还是从事数字IC前端设计、FPGA开发的工程师,本书都是一部极具价值的参考书和提升指南。它能够帮助学习者打下坚实的Verilog语言基础,并建立起面向大规模、复杂数字系统的工程设计方法论。

在“当当网”等平台的普庆图书音像专营店等渠道,读者可以便捷地获取此书并进行在线阅读试读或购买。通过阅读本书的简介与书评,潜在读者可以更好地评估其与自身学习阶段或项目需求的匹配度。

总而言之,《Verilog HDL数字集成电路高级程序设计》是一部聚焦于工程实践能力培养的优秀教材。它犹如一位经验丰富的导师,指引着设计者穿梭于代码与电路之间,最终驾驭Verilog HDL这一强大工具,完成从概念到芯片的精彩创造。在数字技术不断推动时代进步的今天,掌握本书所授的精髓,无疑将为投身于芯片设计行业的学子与专业人士铺就一条坚实的进阶之路。