在当今高性能、低功耗的电子系统需求驱动下,CMOS模拟集成电路的设计面临着前所未有的挑战。传统的基于几何尺寸(如宽长比W/L)的设计方法虽然在直观性上具有优势,但在深亚微米及纳米级工艺下,其与电路实际性能(如跨导gm、速度、噪声)的关联变得复杂且不直接。为此,一种以跨导与漏电流之比(gm/ID)为核心的设计方法学应运而生,它通过将晶体管的偏置状态与性能指标直接关联,为设计师提供了一条更高效、更物理化的设计路径。

一、gm/ID设计方法的核心原理与优势

gm/ID,即跨导效率,是衡量晶体管将电流转换为跨导能力的关键指标。其值范围通常在5到30 V^{-1}之间,直接对应于晶体管的偏置区域:高值对应弱反型区(亚阈值区),低值对应强反型区。该方法的核心思想在于,将gm/ID作为首要设计变量,而非传统的W/L。通过查阅或生成表征特定工艺的“查找表”或特征曲线(如gm/ID vs. ID/(W/L)、ft vs. gm/ID等),设计师可以:

- 直观权衡性能:直接根据所需的增益(gm)、带宽(ft)、噪声等指标,确定最优的gm/ID工作点。

- 实现尺寸无关设计:先确定电流和gm/ID,再反算所需的W/L,使设计过程与工艺特性紧密结合。

- 简化低电压设计:在电源电压不断降低的背景下,该方法便于在弱反型区进行低压低功耗设计。

二、基于gm/ID的设计流程

一个典型的设计流程包括:

- 规格定义与分解:根据系统要求,确定电路级的关键指标,如增益、带宽、功耗、噪声等。

- 选择偏置点(gm/ID):根据速度(ft)、本征增益(gm/gds)等与gm/ID的关系曲线,选择能同时满足多项约束的最佳工作区域。例如,高增益要求可能选择较高的gm/ID(弱反型区),而高带宽要求可能选择较低的gm/ID(强反型区)。

- 确定电流与尺寸:由跨导gm要求(如增益设定)和选定的gm/ID值,计算所需偏置电流ID。利用ID/(W/L)与gm/ID的关系曲线,确定晶体管的尺寸W/L。

- 验证与迭代:利用得到的设计参数进行仿真验证,并微调以满足所有规格。

三、支持gm/ID方法学的软件开发与应用

该设计方法的高效实施严重依赖于软件工具的支撑,其软件开发与应用主要体现在以下几个层面:

1. 工艺特征数据提取与建模软件:

这是基础性工具。软件通过自动化脚本控制SPICE仿真器,对工艺设计套件(PDK)中的晶体管进行大规模直流和AC扫描,生成涵盖各种尺寸、偏压条件下的完整数据集,并拟合生成以gm/ID为自变量的紧凑模型或查找表。此类软件(如自行开发的脚本或专业工具)的准确性直接决定了设计方法的质量。

2. 设计辅助与自动化工具:

这是核心应用软件。它们将上述工艺数据可视化、工具化,例如:

- 交互式设计探索平台:提供图形界面,允许设计师拖动gm/ID滑块,实时观察增益、带宽、功耗等关键参数的变化,进行快速权衡分析。

- 自动尺寸生成器:输入电路拓扑和性能规格(如增益带宽积、相位裕度),工具基于gm/ID方法自动计算所有晶体管的偏置电流和尺寸,大幅缩短设计周期。

- 性能空间映射工具:将电路性能(如噪声、线性度)映射到以gm/ID和电流密度为坐标的二维平面上,帮助直观定位最优设计区域。

3. 与主流EDA工具的集成:

gm/ID设计工具并非要取代SPICE仿真器,而是与其互补。先进的软件开发会注重与Cadence Virtuoso、Synopsys Custom Compiler等商业EDA环境的集成。例如,通过SKILL或Python API,将gm/ID尺寸计算结果直接推送到原理图或版图工具中,或从仿真结果中反向提取数据来丰富特征库,形成闭环设计流程。

4. 教育与应用推广软件:

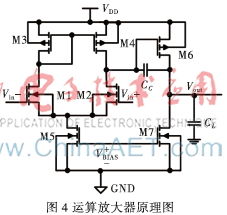

为促进该方法学的普及,开发具有友好界面的教学软件,内置典型工艺库和经典电路案例(如运算放大器、基准电压源),供学生和初学者交互式学习,理解gm/ID如何影响电路行为。

四、应用实例与未来展望

在运算放大器、带隙基准、低压低功耗传感器前端等电路设计中,gm/ID方法已证明其卓越性。它尤其适用于需要精细功耗性能权衡的物联网(IoT)芯片、生物医疗电子等领域。

随着工艺节点持续演进和电路复杂度提升,支持gm/ID方法的软件开发将朝向更智能化、云原生的方向发展:利用机器学习算法从历史设计数据和工艺特征中学习,预测最优设计点;通过云平台提供在线的、工艺无关的初始设计服务,使设计师能更专注于架构创新和系统优化。

基于gm/ID的CMOS模拟集成电路设计方法提供了一种强大且直观的物理洞察力,而围绕其开发的软件工具链则是将这种方法论转化为实际生产力的关键桥梁,共同推动着模拟IC设计向更高效、更可靠的方向迈进。